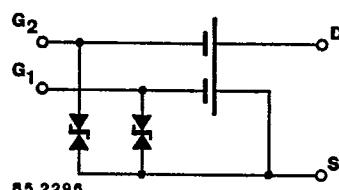

## N-Channel Dual Gate MOS-Fieldeffect Tetrode · Depletion Mode

Applications: Input- and Mixerstages especially for UHF TV-tuners up to 900 MHz

## Features:

- Integrated Gate protection diodes

- High cross modulation performance

- Low noise figure

- High AGC-range

- Low feedback capacitance

- Low input capacitance

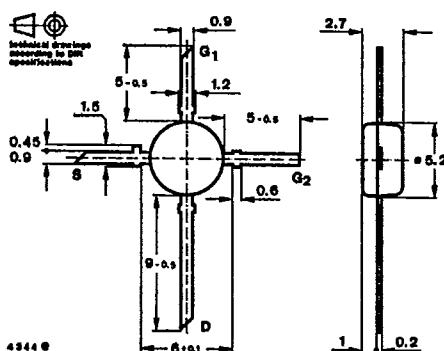

## Dimensions in mm

Case

50 B 4 DIN 41867

JEDEC TO 50

Weight max. 0.1 g

## Absolute maximum ratings

|                                                         |                  |              |    |

|---------------------------------------------------------|------------------|--------------|----|

| Drain Source Voltage                                    | $V_{DS}$         | 20           | V  |

| Drain current                                           | $I_D$            | 30           | mA |

| Gate 1/Gate 2-Source peak current                       | $\pm I_{G1/2SM}$ | 10           | mA |

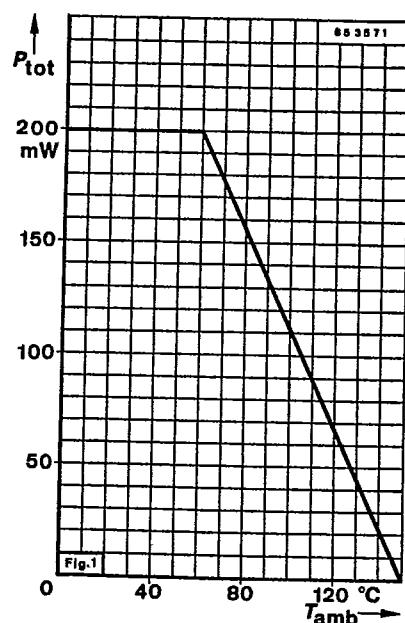

| Total power dissipation<br>$T_{amb} = 60^\circ\text{C}$ | $P_{tot}$        | 200          | mW |

| Channel temperature                                     | $T_C$            | 150          | °C |

| Storage temperature range                               | $T_{stg}$        | -55 ... +150 | °C |

## Thermal resistance

| Channel ambient<br>mounted on pc-board one side<br>Cu 35 $\mu\text{m}$ thickness 40 x 25 x 1.5 mm <sup>3</sup> | $R_{thCA}$ | Min. | Typ. | Max. |

|----------------------------------------------------------------------------------------------------------------|------------|------|------|------|

|                                                                                                                |            | 450  | K/W  |      |

T1.2/330.1183 E2

3523 6-04

BF 960

T-31-25

## DC characteristics

$T_{amb} = 25^\circ C$ , unless otherwise specified

Drain-source breakdown voltage

$I_D = 10 \mu A, -V_{G1S} = -V_{G2S} = 4 V$  $V_{(BR)DS}$  Min. 20 Typ. V Max.

Gate 1-Source breakdown voltage

$\pm I_{G1S} = 10 \text{ mA}, V_{G2S} = V_{DS} = 0$  $\pm V_{(BR)G1SS}$  Min. 6 Typ. 20 V Max.

Gate 2-Source breakdown voltage

$\pm I_{G2S} = 10 \text{ mA}, V_{G1S} = V_{DS} = 0$  $\pm V_{(BR)G2SS}$  Min. 6 Typ. 20 V Max.

Gate 1-Source cut-off current

$\pm V_{G1S} = 5 V, V_{G2S} = V_{DS} = 0$  $I_{G1SS}$  Min. 50 nA

Gate 2-Source cut-off current

$\pm V_{G2S} = 5 V, V_{G1S} = V_{DS} = 0$  $I_{G2SS}$  Min. 50 nA

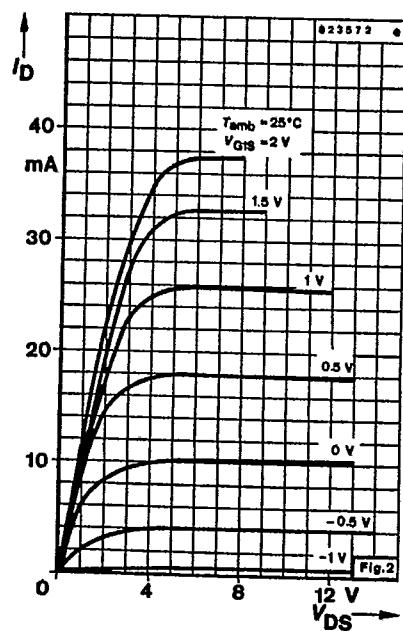

Drain current

$V_{DS} = 15 V, V_{G1S} = 0, V_{G2S} = 4 V$  $I_{DSS}$  Min. 2 Typ. 20 mA

Gate 1-Source cut-off voltage

$V_{DS} = 15 V, V_{G2S} = 4 V, I_D = 20 \mu A$  $-V_{G1S(OFF)}$  Min. 2.7 V

Gate 2-Source cut-off voltage

$V_{DS} = 15 V, V_{G1S} = 0 V, I_D = 20 \mu A$  $-V_{G2S(OFF)}$  Min. 2.7 V

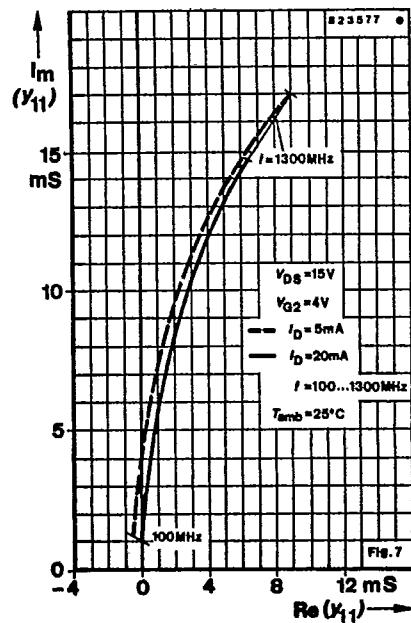

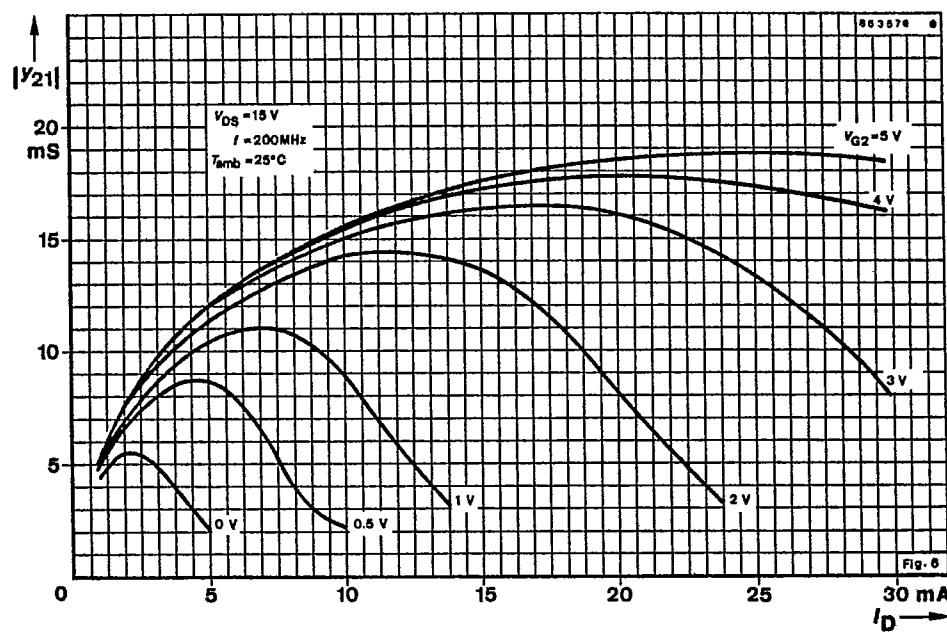

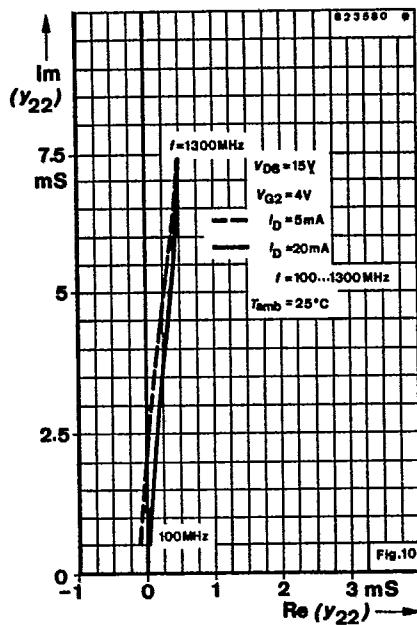

## AC characteristics

$V_{DS} = 15 V, I_D = 7 \text{ mA}, V_{G2S} = 4 V, f = 1 \text{ MHz},$  $T_{amb} = 25^\circ C$ , unless otherwise specified

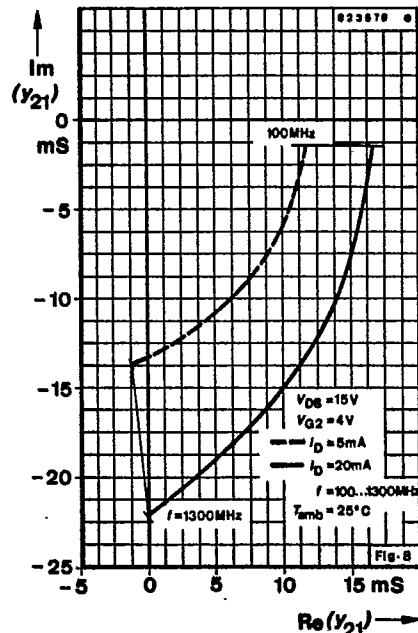

Forward transadmittance

$|y_{21}|$  Min. 10 Typ. 13 mS

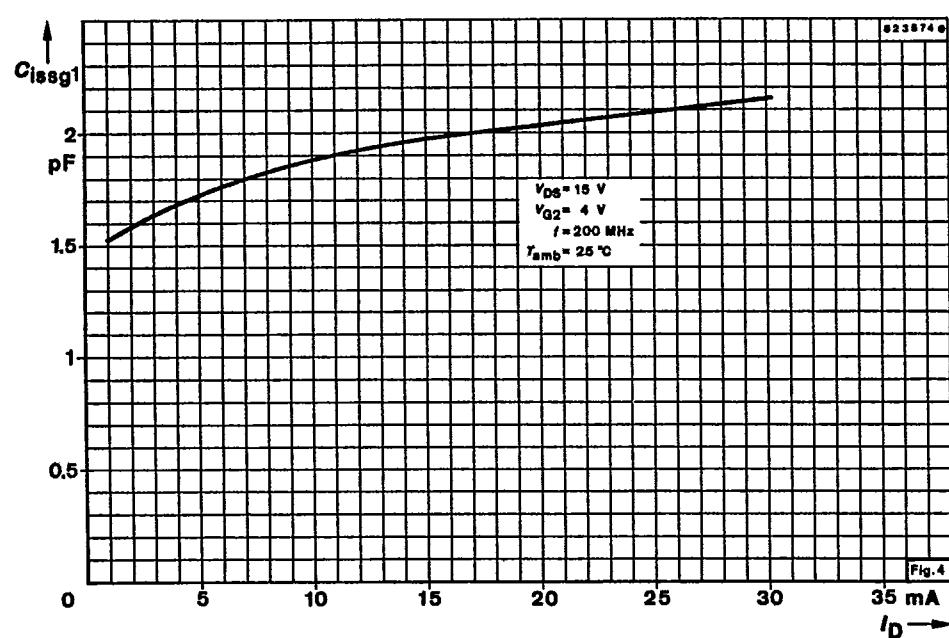

Gate 1-Input capacitance

$C_{ISSG1}$  Min. 1.8 pF

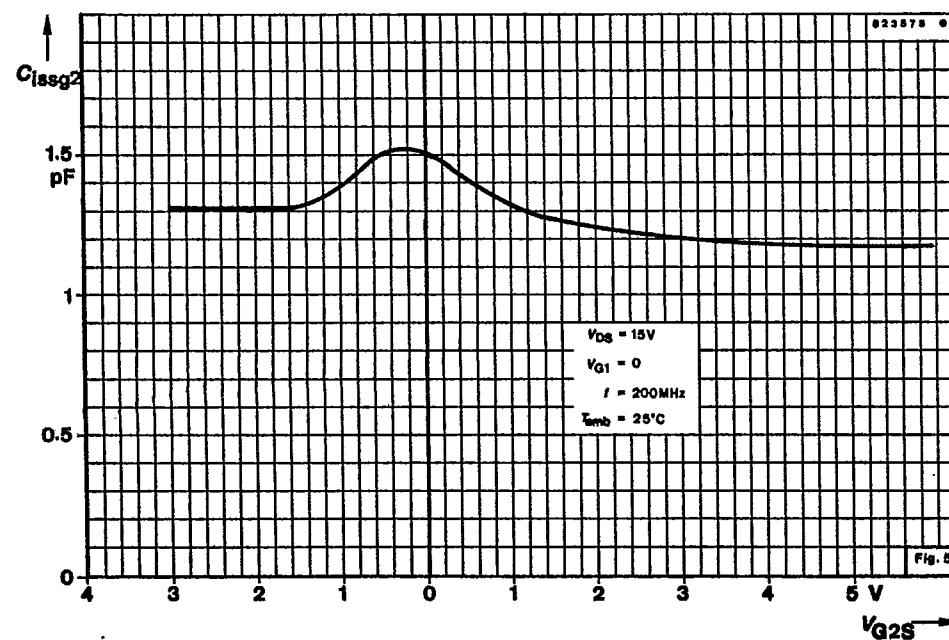

Gate 2-Input capacitance

$V_{G1S} = 0, V_{G2S} = 4 V$   $C_{ISSG2}$  Min. 1.0 pF

Feedback capacitance

$C_{rss}^{1)}$  Min. 25 fF

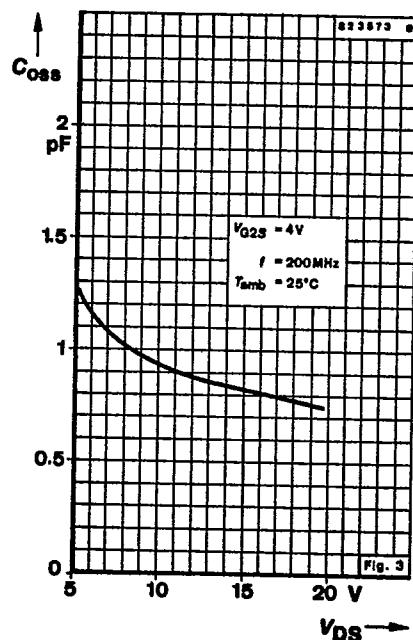

Output capacitance

$C_{oss}$  Min. 0.8 pF

Power gain

$V_{DS} = 15 V, I_D = 7 \text{ mA}, V_{G2S} = 4 V, g_G = 2 \text{ mS},$  $g_L = 5 \text{ mS}, f = 200 \text{ MHz}$  $g_L = 1 \text{ mS}, f = 800 \text{ MHz}$  $G_{ps}$  Min. 23 dB $G_{ps}$  Min. 16.5 dB

Noise figure

$g_G = 2 \text{ mS}, f = 800 \text{ MHz}$  $F$  Min. 2.2 $V_{DS} = 15 V, I_D = 7 \text{ mA}, V_{G2S} = 4 V, V_{G1S} = 0$

3 dB

<sup>1)</sup>  $G_2$  and S grounded

T-31-25

BF 960

3525

6-06

85

BF 960

T-31-25

T-31-25 BF 960

BF 960

T-31-25

T-31-25

BF 960

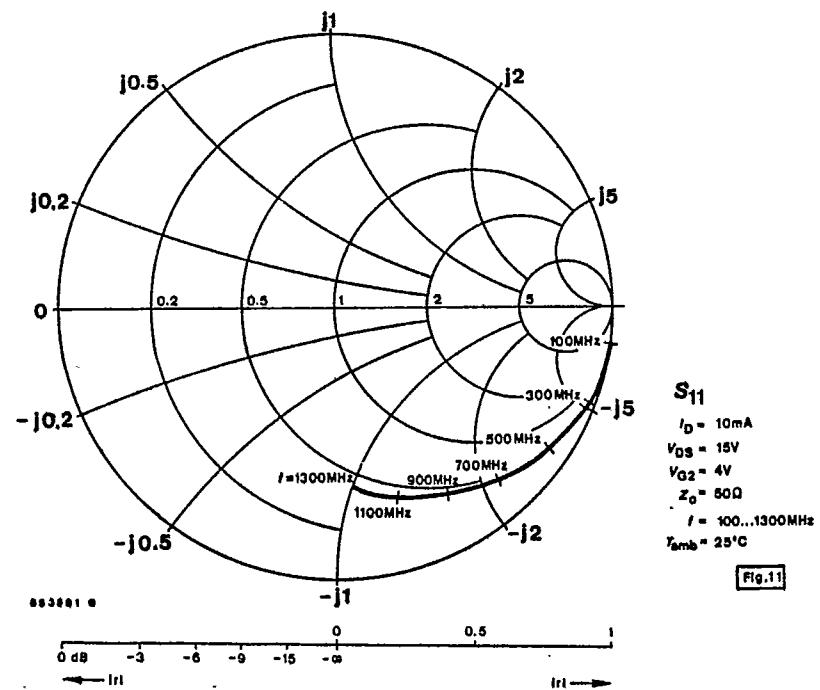

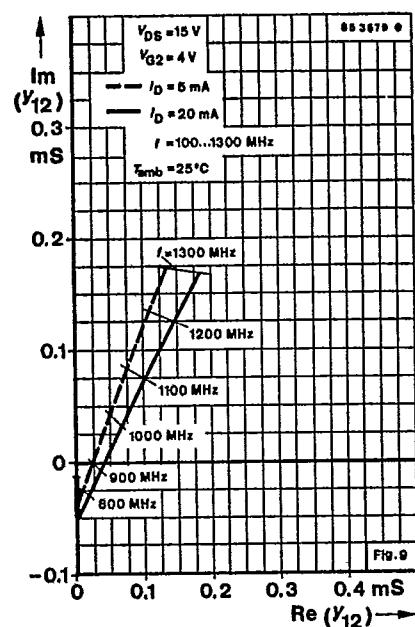

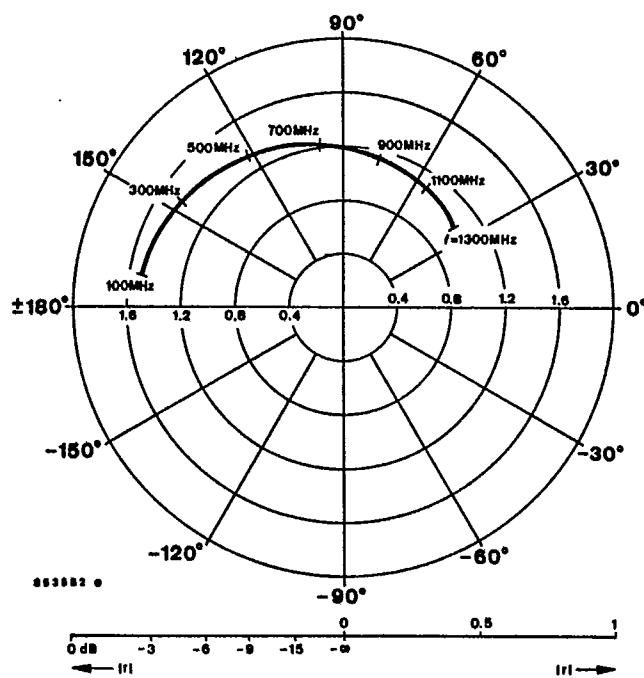

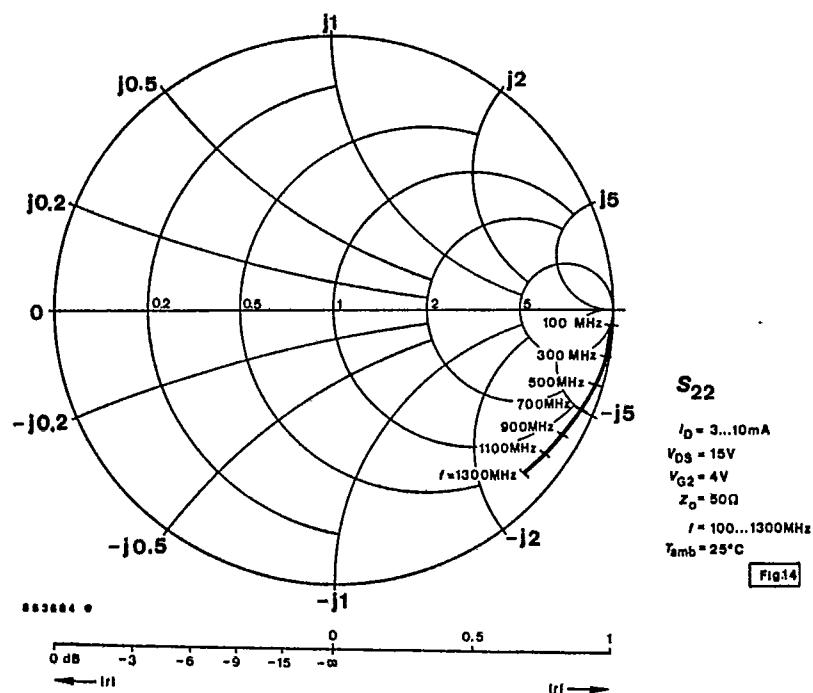

$S_{21}$

$Z_0 = 50\Omega$

$V_{DS} = 15V$

$V_{GS} = 4V$

$I_D = 10mA$

$f = 100...1300MHz$

$T_{amb} = 25^\circ C$

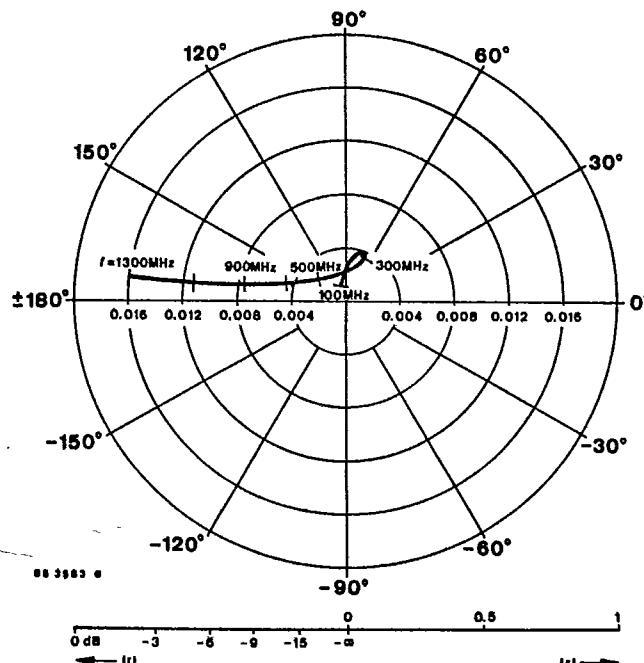

$S_{12}$

$Z_0 = 50\Omega$

$V_{DS} = 15V$

$V_{GS} = 4V$

$I_D = 10mA$

$f = 100...1300MHz$

$T_{amb} = 25^\circ C$

T-31-25

## 7. Taping and Reeling

T-91-20

## 7.1. Taping of TO-92 Transistors

Standard reeling: Taped on reel, reeled together with a paper film.

## 7.1.1. Order Numbers

Add the taping-code to the order number.

## Example:

|                                                 |          |    |    |   |

|-------------------------------------------------|----------|----|----|---|

| Order-No. of Type                               | BC 238 C | DU | 06 | Z |

| Code for TO-92 Transistors                      |          |    |    |   |

| Orientation of transistor on tape <sup>1)</sup> |          |    |    |   |

| Additional marking for specials <sup>2)</sup>   |          |    |    |   |

<sup>1)</sup> 06 = View on flat side of transistor, view on gummed tape

05 = View on round side of transistor, view on gummed tape

<sup>2)</sup> Additional marking "0": taping without paper film

Additional marking "Z": Zigzag folded tape in special box. Marking for orientation of transistor not necessary, because box can be opened on top or bottom

Example for order No.: BC 237 C DU Z

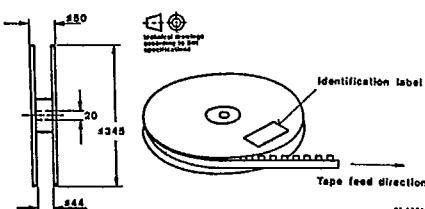

Fig. 7.1. Dimensions of reel in mm

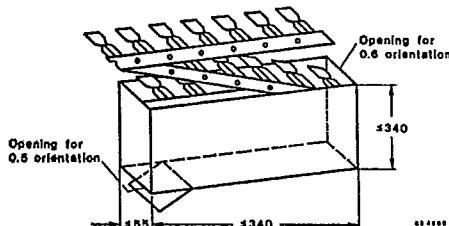

Fig. 7.2. Dimension of box for Zigzag folding in mm

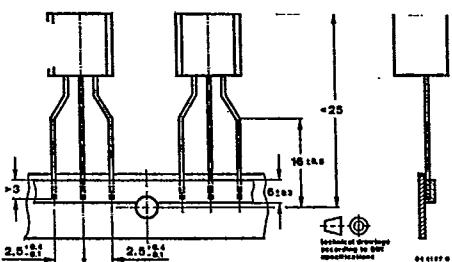

Fig. 7.3 Dimensions of tape in mm

## 7.1.2. Quantity of devices

1000 devices per reel

2000 devices per folded tape in special box.

## 7.2. Taped transistors in SOT 23 and SOT 143 case

## 7.2.1. Designation

## a) Standard taping

Designation is attached with code GS 08 in case of standard taping. Example for normal version transistors as standard taped: BF 569-GS 08.

Example for R-version transistors as standard taped: BF 569 R-GS 08.

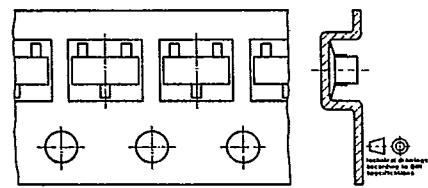

In case of standard taping, the transistor orientation on the tape is shown in Fig. 7.4 and Fig. 7.5.

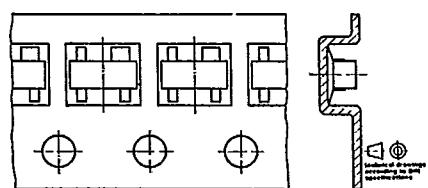

Fig. 7.4 Standard taped SOT 23

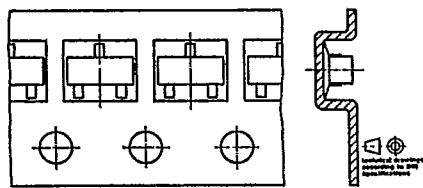

Fig. 7.5. Standard taped SOT 143

T-91-20

## b) Reverse taping

Designation is attached with code GS 07 in case of reverse taping. Example for normal version transistors as reverse taped: BF 569-GS 07.

Example for R-version transistors as reverse taping: BF 569 R-GS 07.

In case of reverse taping, the transistor orientation on the tape is shown in Fig. 7.6.

Regarding MOS-FET and MES-FET devices, reverse taping is at present not available.

Fig. 7.6 Reverse taped SOT 23

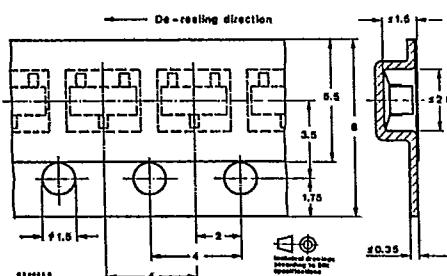

Fig. 7.7 Dimensions of tape in mm

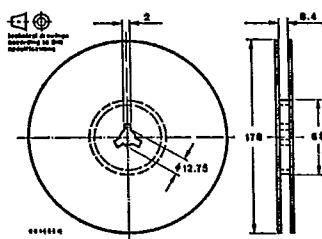

Fig. 7.8 Dimensions of reel in mm

## 7.2.2 Quantity of devices

3000 devices per reel