HUF75645S3S Specs and Replacement

Type Designator: HUF75645S3S

Type of Transistor: MOSFET

Type of Control Channel: N-Channel

Absolute Maximum Ratings

Pd ⓘ

- Maximum Power Dissipation: 310 W

|Vds|ⓘ - Maximum Drain-Source Voltage: 100 V

|Vgs|ⓘ - Maximum Gate-Source Voltage: 20 V

|Id| ⓘ - Maximum Drain Current: 75 A

Tj ⓘ - Maximum Junction Temperature: 150 °C

Electrical Characteristics

Rds ⓘ - Maximum Drain-Source On-State Resistance: 0.014 Ohm

Package: TO263AB

- MOSFET ⓘ Cross-Reference Search

HUF75645S3S datasheet

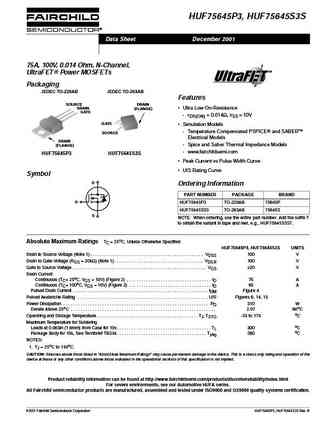

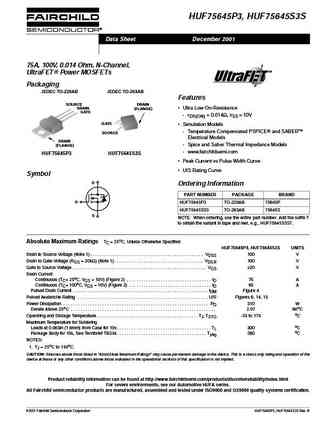

..1. Size:204K fairchild semi

huf75645p3 huf75645s3s.pdf

HUF75645P3, HUF75645S3S Data Sheet December 2001 75A, 100V, 0.014 Ohm, N-Channel, UltraFET Power MOSFETs Packaging JEDEC TO-220AB JEDEC TO-263AB Features SOURCE DRAIN DRAIN Ultra Low On-Resistance (FLANGE) GATE - rDS(ON) = 0.014 , VGS = 10V GATE Simulation Models - Temperature Compensated PSPICE and SABER SOURCE Electrical Models DRAIN - Spice and Saber Th... See More ⇒

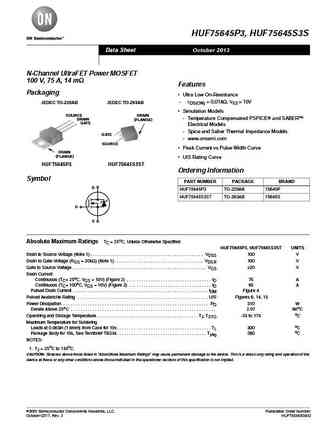

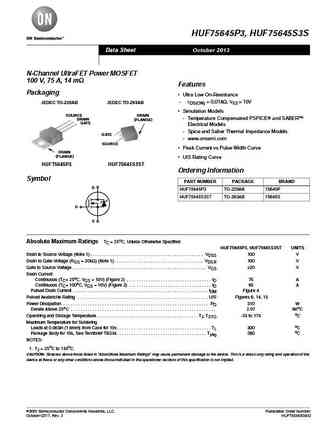

..2. Size:391K onsemi

huf75645p3 huf75645s3s.pdf

HUF75645P3, HUF75645S3S Data Sheet October 2013 N-Channel UltraFET Power MOSFET 100 V, 75 A, 14 m Features Packaging Ultra Low On-Resistance - rDS(ON) = 0.014 , VGS = 10V JEDEC TO-220AB JEDEC TO-263AB Simulation Models SOURCE DRAIN - Temperature Compensated PSPICE and SABER DRAIN (FLANGE) GATE Electrical Models - Spice and Saber Thermal Impedance Models GATE... See More ⇒

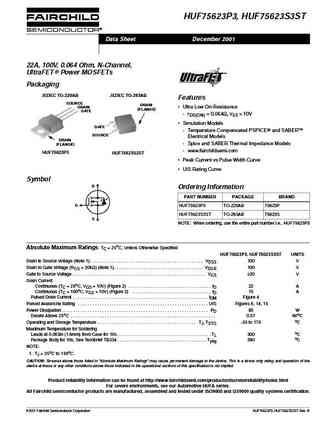

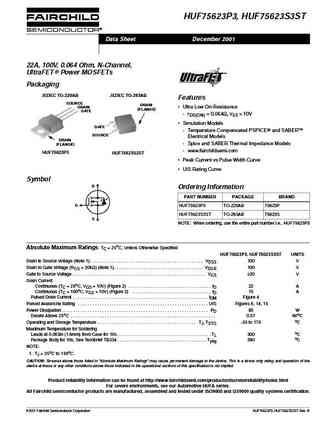

0.1. Size:203K fairchild semi

huf75645s3st.pdf

HUF75645P3, HUF75645S3S Data Sheet December 2001 75A, 100V, 0.014 Ohm, N-Channel, UltraFET Power MOSFETs Packaging JEDEC TO-220AB JEDEC TO-263AB Features SOURCE DRAIN DRAIN Ultra Low On-Resistance (FLANGE) GATE - rDS(ON) = 0.014 , VGS = 10V GATE Simulation Models - Temperature Compensated PSPICE and SABER SOURCE Electrical Models DRAIN - Spice and Saber Th... See More ⇒

8.1. Size:198K fairchild semi

huf75623s3st.pdf

HUF75623P3, HUF75623S3ST Data Sheet December 2001 22A, 100V, 0.064 Ohm, N-Channel, UltraFET Power MOSFETs Packaging JEDEC TO-220AB JEDEC TO-263AB Features SOURCE DRAIN DRAIN Ultra Low On-Resistance (FLANGE) GATE - rDS(ON) = 0.064 , VGS = 10V Simulation Models GATE - Temperature Compensated PSPICE and SABER SOURCE Electrical Models DRAIN - Spice and SABER T... See More ⇒

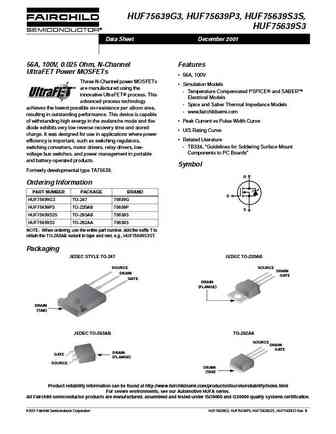

8.2. Size:227K fairchild semi

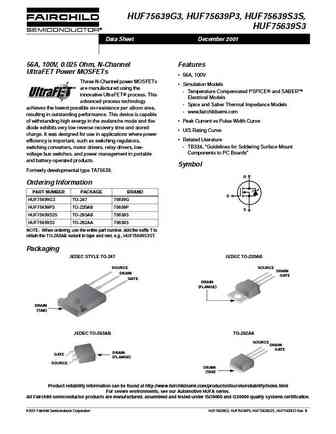

huf75639s3st.pdf

HUF75639G3, HUF75639P3, HUF75639S3S, HUF75639S3 Data Sheet December 2001 56A, 100V, 0.025 Ohm, N-Channel Features UltraFET Power MOSFETs 56A, 100V These N-Channel power MOSFETs Simulation Models are manufactured using the - Temperature Compensated PSPICE and SABER innovative UltraFET process. This Electrical Models advanced process technology - Spice and Saber T... See More ⇒

8.3. Size:254K fairchild semi

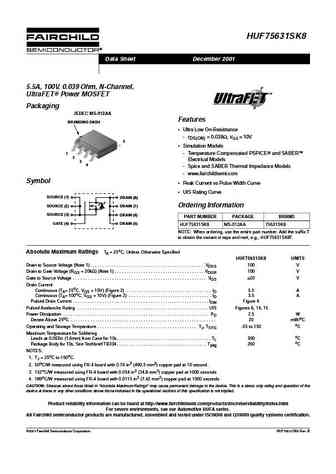

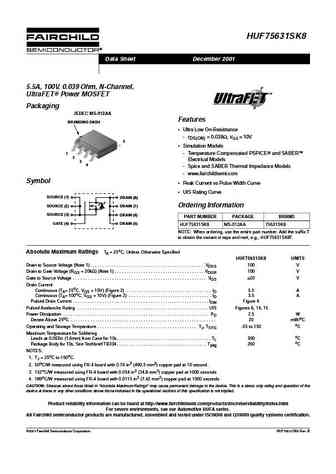

huf75631sk8.pdf

HUF75631SK8 Data Sheet December 2001 5.5A, 100V, 0.039 Ohm, N-Channel, UltraFET Power MOSFET Packaging JEDEC MS-012AA Features BRANDING DASH Ultra Low On-Resistance - rDS(ON) = 0.039 , VGS = 10V 5 Simulation Models 1 - Temperature Compensated PSPICE and SABER 2 Electrical Models 3 4 - Spice and SABER Thermal Impedance Models - www.fairchildsemi.com Symbol ... See More ⇒

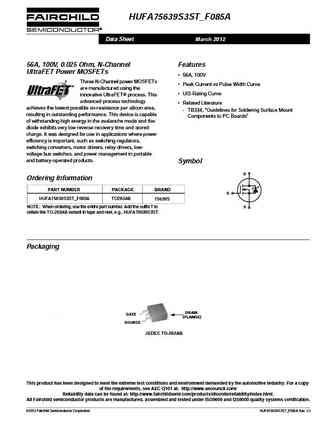

8.4. Size:230K fairchild semi

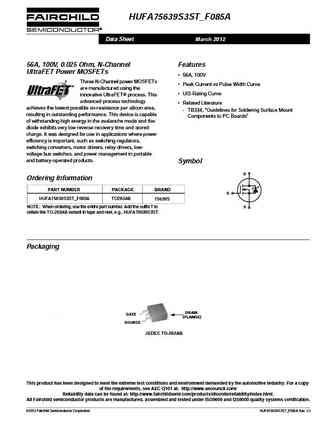

huf75639s f085a.pdf

HUFA75639S3ST_F085A Data Sheet March 2012 56A, 100V, 0.025 Ohm, N-Channel Features UltraFET Power MOSFETs 56A, 100V These N-Channel power MOSFETs Peak Current vs Pulse Width Curve are manufactured using the UIS Rating Curve innovative UltraFET process. This advanced process technology Related Literature achieves the lowest possible on-resistance per silicon ar... See More ⇒

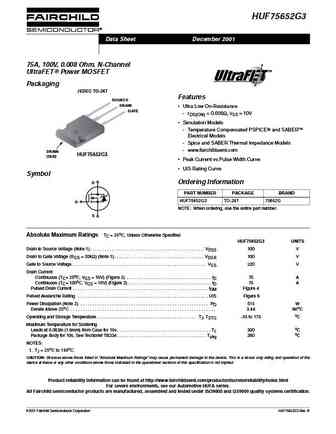

8.5. Size:195K fairchild semi

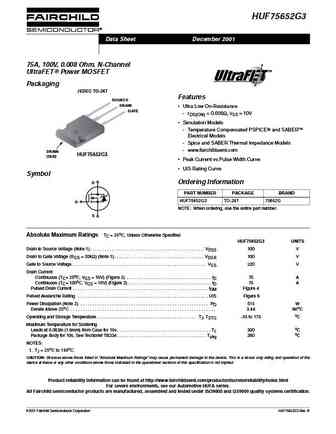

huf75652g3.pdf

HUF75652G3 Data Sheet December 2001 75A, 100V, 0.008 Ohm, N-Channel UltraFET Power MOSFET Packaging JEDEC TO-247 Features SOURCE DRAIN Ultra Low On-Resistance GATE - rDS(ON) = 0.008 , VGS = 10V Simulation Models - Temperature Compensated PSPICE and SABER Electrical Models - Spice and SABER Thermal Impedance Models - www.fairchildsemi.com DRAIN HUF75652G3 (T... See More ⇒

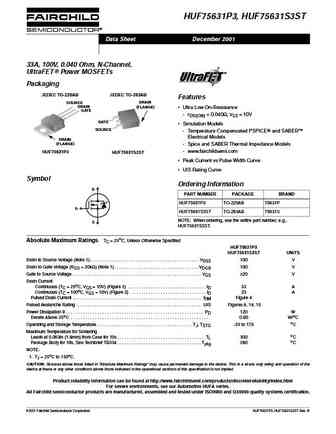

8.6. Size:202K fairchild semi

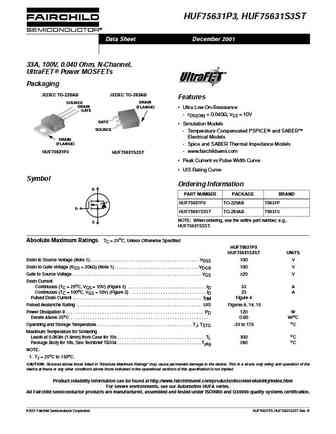

huf75631s3s.pdf

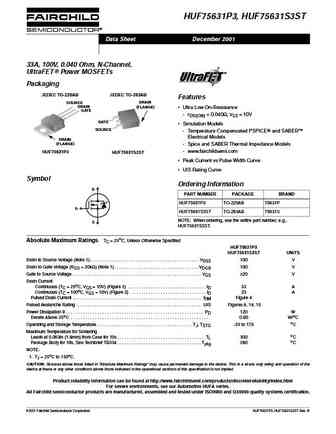

HUF75631P3, HUF75631S3ST Data Sheet December 2001 33A, 100V, 0.040 Ohm, N-Channel, UltraFET Power MOSFETs Packaging JEDEC TO-220AB JEDEC TO-263AB Features SOURCE DRAIN DRAIN (FLANGE) Ultra Low On-Resistance GATE - rDS(ON) = 0.040 , VGS = 10V GATE Simulation Models SOURCE - Temperature Compensated PSPICE and SABER Electrical Models DRAIN (FLANGE) - Spice an... See More ⇒

8.7. Size:249K fairchild semi

huf75631sk8t.pdf

HUF75631SK8 Data Sheet December 2001 5.5A, 100V, 0.039 Ohm, N-Channel, UltraFET Power MOSFET Packaging JEDEC MS-012AA Features BRANDING DASH Ultra Low On-Resistance - rDS(ON) = 0.039 , VGS = 10V 5 Simulation Models 1 - Temperature Compensated PSPICE and SABER 2 Electrical Models 3 4 - Spice and SABER Thermal Impedance Models - www.fairchildsemi.com Symbol ... See More ⇒

8.8. Size:200K fairchild semi

huf75637s3 huf75637s3st.pdf

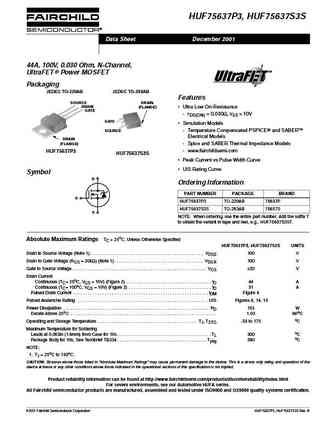

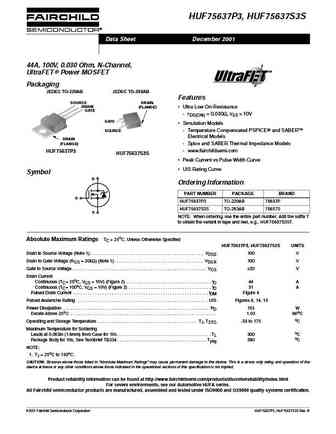

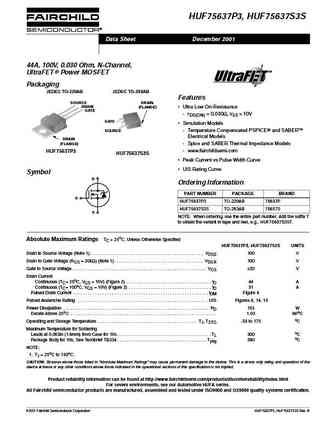

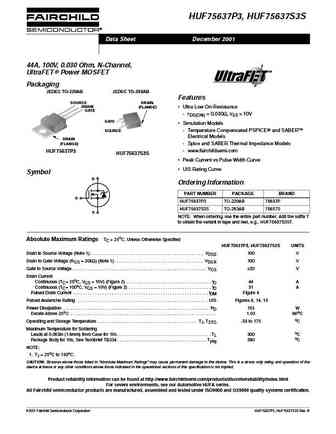

HUF75637P3, HUF75637S3S Data Sheet December 2001 44A, 100V, 0.030 Ohm, N-Channel, UltraFET Power MOSFET Packaging JEDEC TO-220AB JEDEC TO-263AB Features SOURCE DRAIN DRAIN (FLANGE) Ultra Low On-Resistance GATE - rDS(ON) = 0.030 , VGS = 10V GATE Simulation Models SOURCE - Temperature Compensated PSPICE and SABER Electrical Models DRAIN (FLANGE) - Spice and S... See More ⇒

8.9. Size:201K fairchild semi

huf75637.pdf

HUF75637P3, HUF75637S3S Data Sheet December 2001 44A, 100V, 0.030 Ohm, N-Channel, UltraFET Power MOSFET Packaging JEDEC TO-220AB JEDEC TO-263AB Features SOURCE DRAIN DRAIN (FLANGE) Ultra Low On-Resistance GATE - rDS(ON) = 0.030 , VGS = 10V GATE Simulation Models SOURCE - Temperature Compensated PSPICE and SABER Electrical Models DRAIN (FLANGE) - Spice and S... See More ⇒

8.10. Size:229K fairchild semi

huf75639g3 huf75639p3 huf75639s3s huf75639s3.pdf

HUF75639G3, HUF75639P3, HUF75639S3S, HUF75639S3 Data Sheet December 2001 56A, 100V, 0.025 Ohm, N-Channel Features UltraFET Power MOSFETs 56A, 100V These N-Channel power MOSFETs Simulation Models are manufactured using the - Temperature Compensated PSPICE and SABER innovative UltraFET process. This Electrical Models advanced process technology - Spice and Saber T... See More ⇒

8.11. Size:196K fairchild semi

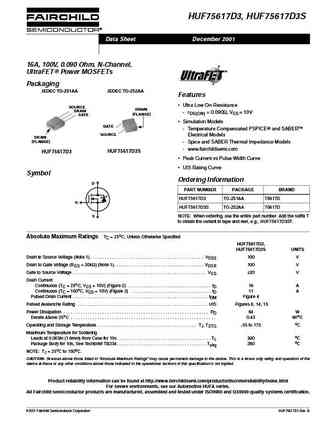

huf75617d3st huf75617d3 huf75617d3s.pdf

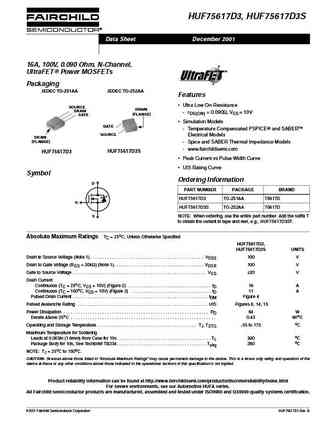

HUF75617D3, HUF75617D3S Data Sheet December 2001 16A, 100V, 0.090 Ohm, N-Channel, UltraFET Power MOSFETs Packaging JEDEC TO-251AA JEDEC TO-252AA Features Ultra Low On-Resistance SOURCE DRAIN DRAIN - rDS(ON) = 0.090 , VGS = 10V (FLANGE) GATE Simulation Models GATE - Temperature Compensated PSPICE and SABER SOURCE Electrical Models DRAIN (FLANGE) - Spice ... See More ⇒

8.12. Size:200K fairchild semi

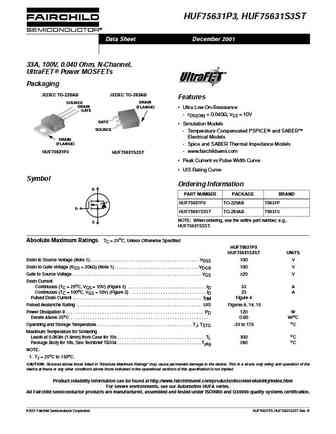

huf75631s3st.pdf

HUF75631P3, HUF75631S3ST Data Sheet December 2001 33A, 100V, 0.040 Ohm, N-Channel, UltraFET Power MOSFETs Packaging JEDEC TO-220AB JEDEC TO-263AB Features SOURCE DRAIN DRAIN (FLANGE) Ultra Low On-Resistance GATE - rDS(ON) = 0.040 , VGS = 10V GATE Simulation Models SOURCE - Temperature Compensated PSPICE and SABER Electrical Models DRAIN (FLANGE) - Spice an... See More ⇒

8.13. Size:537K onsemi

huf75652g3.pdf

MOSFET Power, N-Channel, Ultrafet 100 V, 75 A, 8 mW HUF75652G3 Features www.onsemi.com Ultra Low On-Resistance rDS(ON) = 0.008 W, VGS = 10 V Simulation Models D Temperature Compensated PSPICE and SABER Electrical Models Spice and SABER Thermal Impedance Models G www.onsemi.com Peak Current vs Pulse Width Curve S UIS Rating Curve Th... See More ⇒

8.14. Size:720K onsemi

huf75639g3 huf75639p3 huf75639s3s huf75639s3.pdf

MOSFET Power, N-Channel, Ultrafet 100 V, 56 A, 25 mW HUF75639G3, HUF75639P3, HUF75639S3S, HUF75639S3 www.onsemi.com These N-Channel power MOSFETs are manufactured using the innovative Ultrafet process. This advanced process technology achieves the lowest possible on- resistance per silicon area, resulting in outstanding performance. This device is capable of withstanding high ener... See More ⇒

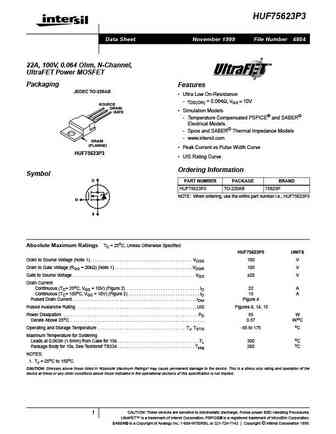

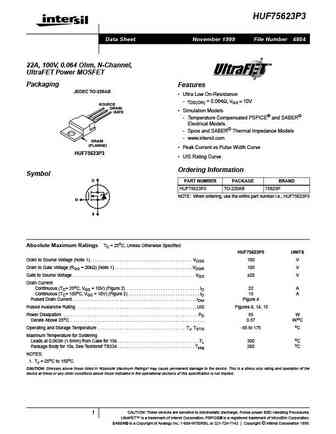

8.15. Size:98K intersil

huf75623p3.pdf

HUF75623P3 Data Sheet November 1999 File Number 4804 22A, 100V, 0.064 Ohm, N-Channel, UltraFET Power MOSFET Packaging Features JEDEC TO-220AB Ultra Low On-Resistance - rDS(ON) = 0.064 , VGS = 10V SOURCE DRAIN Simulation Models GATE - Temperature Compensated PSPICE and SABER Electrical Models - Spice and SABER Thermal Impedance Models - www.intersil.com DRAIN (... See More ⇒

Detailed specifications: HUF75631P3

, HUF75631SK8

, HUF75637P3

, HUF75637S3S

, HUF75639G3

, HUF75639P3

, HUF75639S3S

, HUF75645P3

, RU7088R

, HUF75652G3

, HUF76105DK8

, HUF76105SK8

, HUF76107D3

, HUF76107D3S

, HUF76107P3

, HUF76113DK8

, HUF76113SK8

.

Keywords - HUF75645S3S MOSFET specs

HUF75645S3S cross reference

HUF75645S3S equivalent finder

HUF75645S3S pdf lookup

HUF75645S3S substitution

HUF75645S3S replacement

Learn how to find the right MOSFET substitute. A guide to cross-reference, check specs and replace MOSFETs in your circuits.