HUF76609D3ST. Аналоги и основные параметры

Наименование производителя: HUF76609D3ST

Тип транзистора: MOSFET

Полярность: N

Предельные значения

Pd ⓘ

- Максимальная рассеиваемая мощность: 49 W

|Vds|ⓘ - Максимально допустимое напряжение сток-исток: 100 V

|Vgs|ⓘ - Максимально допустимое напряжение затвор-исток: 16 V

|Id| ⓘ - Максимально допустимый постоянный ток стока: 10 A

Tj ⓘ - Максимальная температура канала: 175 °C

Электрические характеристики

tr ⓘ -

Время нарастания: 41 ns

Cossⓘ - Выходная емкость: 75 pf

RDSonⓘ - Сопротивление сток-исток открытого транзистора: 0.16 Ohm

Тип корпуса: TO-252AA

Аналог (замена) для HUF76609D3ST

- подборⓘ MOSFET транзистора по параметрам

HUF76609D3ST даташит

..1. Size:218K fairchild semi

huf76609d3st.pdf

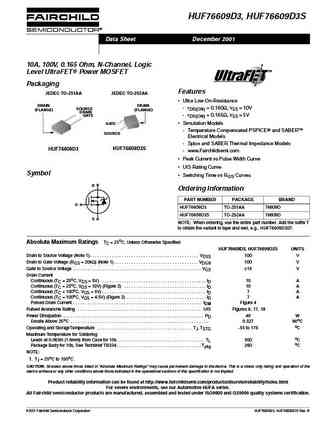

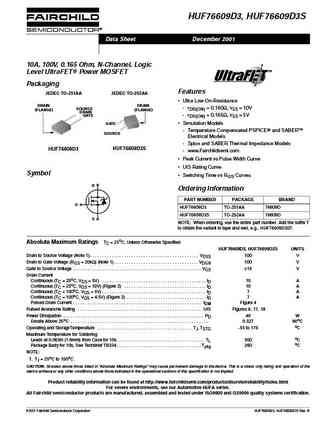

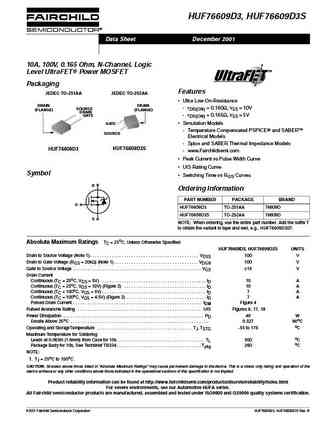

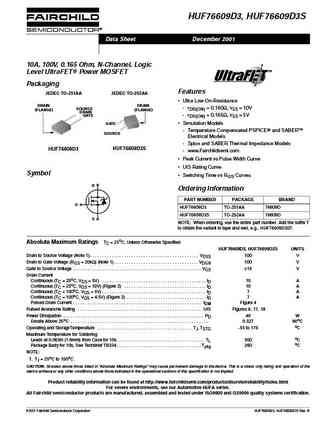

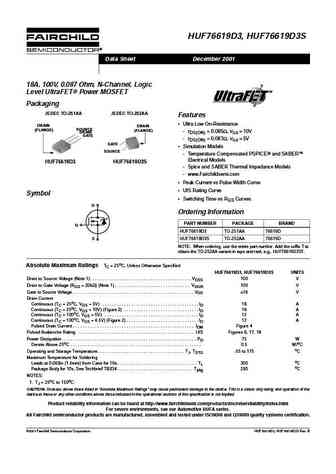

HUF76609D3, HUF76609D3S Data Sheet December 2001 10A, 100V, 0.165 Ohm, N-Channel, Logic Level UltraFET Power MOSFET Packaging Features JEDEC TO-251AA JEDEC TO-252AA Ultra Low On-Resistance DRAIN DRAIN - rDS(ON) = 0.160 , VGS = 10V SOURCE (FLANGE) (FLANGE) DRAIN GATE - rDS(ON) = 0.165 , VGS = 5V GATE Simulation Models - Temperature Compensated PSPICE and SABER

3.1. Size:220K fairchild semi

huf76609d3s.pdf

HUF76609D3, HUF76609D3S Data Sheet December 2001 10A, 100V, 0.165 Ohm, N-Channel, Logic Level UltraFET Power MOSFET Packaging Features JEDEC TO-251AA JEDEC TO-252AA Ultra Low On-Resistance DRAIN DRAIN - rDS(ON) = 0.160 , VGS = 10V SOURCE (FLANGE) (FLANGE) DRAIN GATE - rDS(ON) = 0.165 , VGS = 5V GATE Simulation Models - Temperature Compensated PSPICE and SABER

3.2. Size:844K onsemi

huf76609d3s.pdf

Is Now Part of To learn more about ON Semiconductor, please visit our website at www.onsemi.com Please note As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor s system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclatur

8.1. Size:220K fairchild semi

huf76619d3-s.pdf

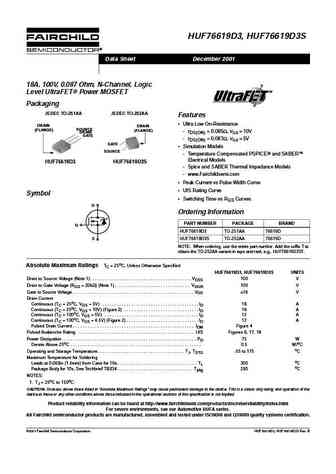

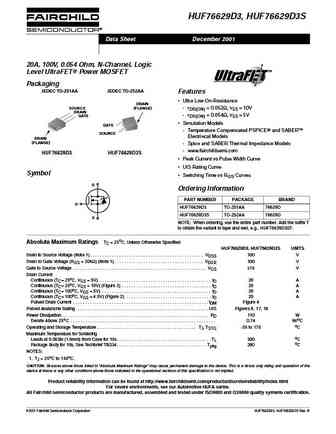

HUF76619D3, HUF76619D3S Data Sheet December 2001 18A, 100V, 0.087 Ohm, N-Channel, Logic Level UltraFET Power MOSFET Packaging JEDEC TO-251AA JEDEC TO-252AA Features Ultra Low On-Resistance DRAIN DRAIN SOURCE (FLANGE) (FLANGE) - rDS(ON) = 0.085 , VGS = 10V DRAIN GATE - rDS(ON) = 0.087 , VGS = 5V GATE Simulation Models SOURCE - Temperature Compensated PSPICE

8.2. Size:201K fairchild semi

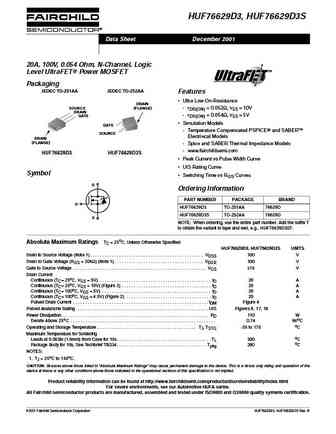

huf76629d3st.pdf

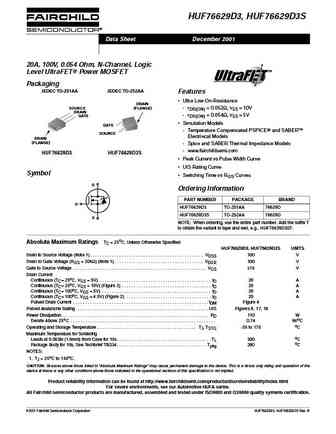

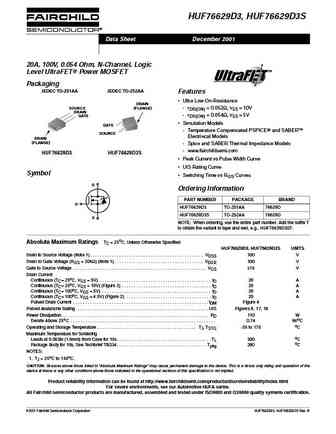

HUF76629D3, HUF76629D3S Data Sheet December 2001 20A, 100V, 0.054 Ohm, N-Channel, Logic Level UltraFET Power MOSFET Packaging JEDEC TO-251AA JEDEC TO-252AA Features Ultra Low On-Resistance DRAIN SOURCE (FLANGE) - rDS(ON) = 0.052 , VGS = 10V DRAIN - rDS(ON) = 0.054 , VGS = 5V GATE Simulation Models GATE - Temperature Compensated PSPICE and SABER SOURCE Elect

8.3. Size:203K fairchild semi

huf76629d3-s.pdf

HUF76629D3, HUF76629D3S Data Sheet December 2001 20A, 100V, 0.054 Ohm, N-Channel, Logic Level UltraFET Power MOSFET Packaging JEDEC TO-251AA JEDEC TO-252AA Features Ultra Low On-Resistance DRAIN SOURCE (FLANGE) - rDS(ON) = 0.052 , VGS = 10V DRAIN - rDS(ON) = 0.054 , VGS = 5V GATE Simulation Models GATE - Temperature Compensated PSPICE and SABER SOURCE Elect

8.4. Size:369K fairchild semi

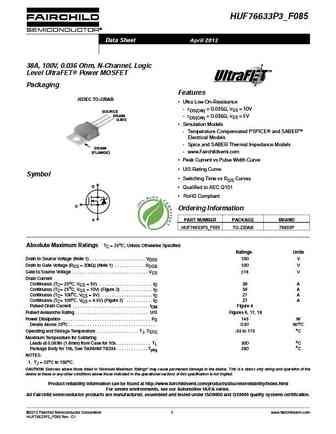

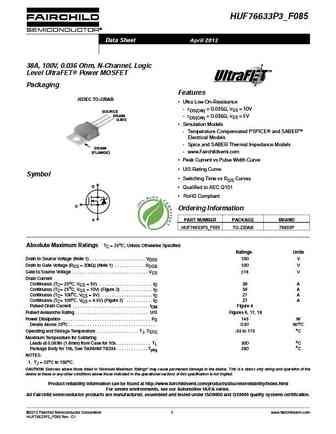

huf76633p3 f085.pdf

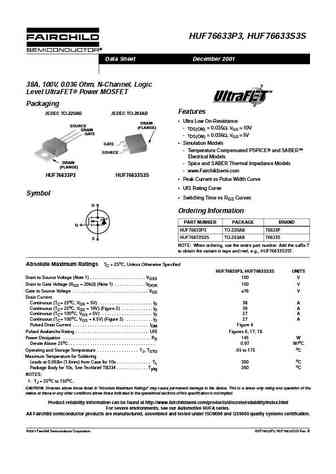

HUF76633P3_F085 Data Sheet April 2012 38A, 100V, 0.036 Ohm, N-Channel, Logic Level UltraFET Power MOSFET Packaging Features JEDEC TO-220AB Ultra Low On-Resistance - rDS(ON) = 0.035 , VGS = 10V SOURCE DRAIN - rDS(ON) = 0.036 , VGS = 5V GATE Simulation Models - Temperature Compensated PSPICE and SABER Electrical Models - Spice and SABER Thermal Impedance Model

8.5. Size:216K fairchild semi

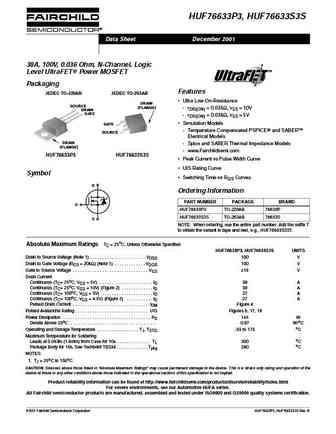

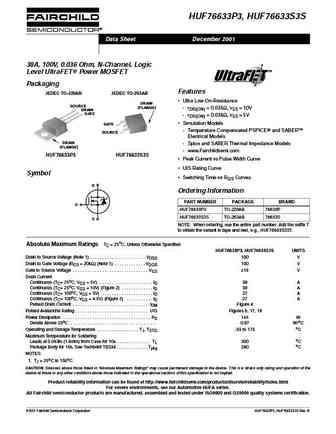

huf76633s3st.pdf

HUF76633P3, HUF76633S3S Data Sheet December 2001 38A, 100V, 0.036 Ohm, N-Channel, Logic Level UltraFET Power MOSFET Packaging Features JEDEC TO-220AB JEDEC TO-263AB Ultra Low On-Resistance DRAIN SOURCE (FLANGE) - rDS(ON) = 0.035 , VGS = 10V DRAIN GATE - rDS(ON) = 0.036 , VGS = 5V Simulation Models GATE - Temperature Compensated PSPICE and SABER SOURCE El

8.6. Size:218K fairchild semi

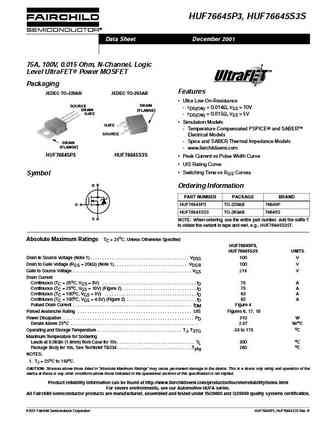

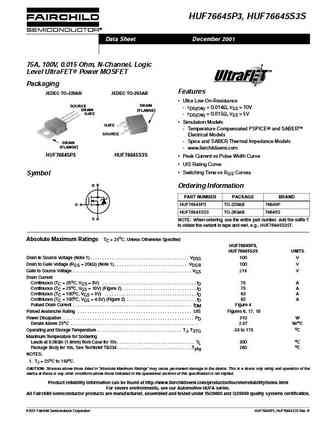

huf76645p3-s3s.pdf

HUF76645P3, HUF76645S3S Data Sheet December 2001 75A, 100V, 0.015 Ohm, N-Channel, Logic Level UltraFET Power MOSFET Packaging Features JEDEC TO-220AB JEDEC TO-263AB Ultra Low On-Resistance DRAIN SOURCE - rDS(ON) = 0.014 , VGS = 10V DRAIN (FLANGE) GATE - rDS(ON) = 0.015 , VGS = 5V Simulation Models GATE - Temperature Compensated PSPICE and SABER SOURCE Elect

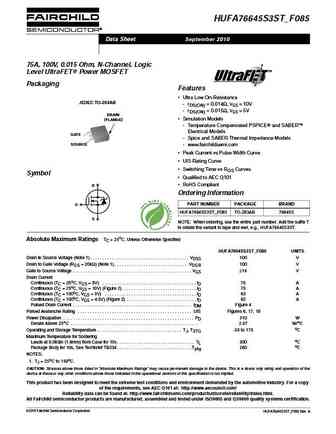

8.7. Size:303K fairchild semi

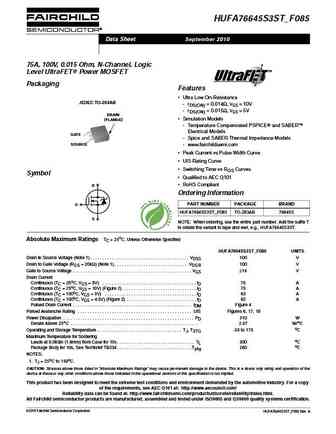

huf76645s f085.pdf

HUFA76645S3ST_F085 Data Sheet September 2010 75A, 100V, 0.015 Ohm, N-Channel, Logic Level UltraFET Power MOSFET Packaging Features Ultra Low On-Resistance JEDEC TO-263AB - rDS(ON) = 0.014 , VGS = 10V - rDS(ON) = 0.015 , VGS = 5V DRAIN Simulation Models (FLANGE) - Temperature Compensated PSPICE and SABER Electrical Models GATE - Spice and SABER Thermal Imped

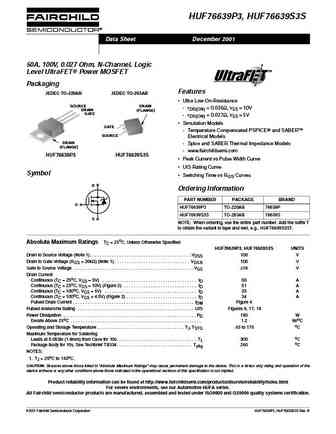

8.8. Size:218K fairchild semi

huf76639s3s.pdf

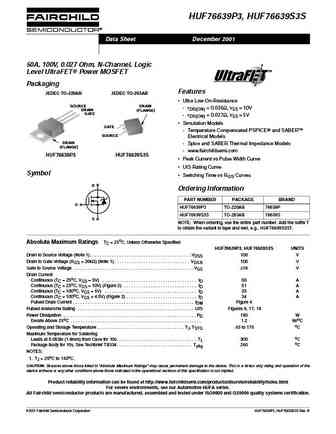

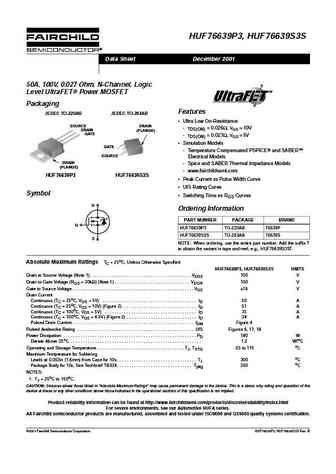

HUF76639P3, HUF76639S3S Data Sheet December 2001 50A, 100V, 0.027 Ohm, N-Channel, Logic Level UltraFET Power MOSFET Packaging Features JEDEC TO-220AB JEDEC TO-263AB Ultra Low On-Resistance SOURCE DRAIN - rDS(ON) = 0.026 , VGS = 10V DRAIN (FLANGE) GATE - rDS(ON) = 0.027 , VGS = 5V Simulation Models GATE - Temperature Compensated PSPICE and SABER SOURCE Ele

8.9. Size:222K fairchild semi

huf76619d3st.pdf

HUF76619D3, HUF76619D3S Data Sheet December 2001 18A, 100V, 0.087 Ohm, N-Channel, Logic Level UltraFET Power MOSFET Packaging JEDEC TO-251AA JEDEC TO-252AA Features Ultra Low On-Resistance DRAIN DRAIN SOURCE (FLANGE) (FLANGE) - rDS(ON) = 0.085 , VGS = 10V DRAIN GATE - rDS(ON) = 0.087 , VGS = 5V GATE Simulation Models SOURCE - Temperature Compensated PSPICE

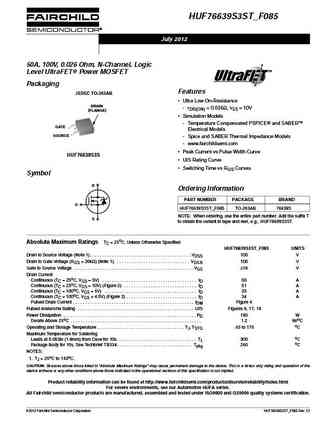

8.10. Size:244K fairchild semi

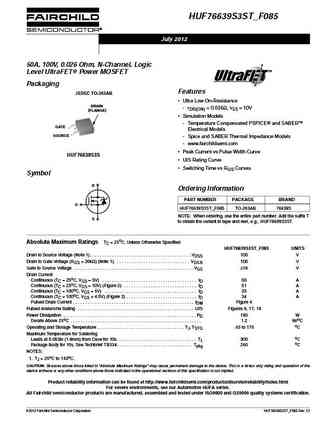

huf76639s f085.pdf

HUF76639S3ST_F085 July 2012 50A, 100V, 0.026 Ohm, N-Channel, Logic Level UltraFET Power MOSFET Packaging Features JEDEC TO-263AB Ultra Low On-Resistance DRAIN - rDS(ON) = 0.026 , VGS = 10V (FLANGE) Simulation Models - Temperature Compensated PSPICE and SABER GATE Electrical Models SOURCE - Spice and SABER Thermal Impedance Models - www.fairchildsemi.com

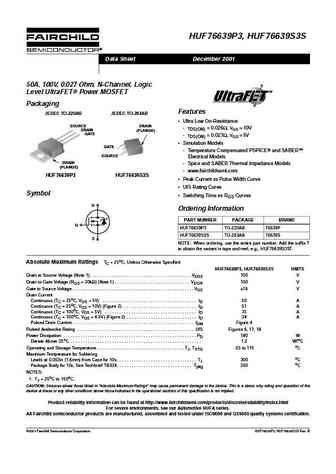

8.11. Size:223K fairchild semi

huf76639p3-s3s.pdf

HUF76639P3, HUF76639S3S Data Sheet December 2001 50A, 100V, 0.027 Ohm, N-Channel, Logic Level UltraFET Power MOSFET Packaging Features JEDEC TO-220AB JEDEC TO-263AB Ultra Low On-Resistance SOURCE DRAIN - rDS(ON) = 0.026 , VGS = 10V DRAIN (FLANGE) GATE - rDS(ON) = 0.027 , VGS = 5V Simulation Models GATE - Temperature Compensated PSPICE and SABER SOURCE Ele

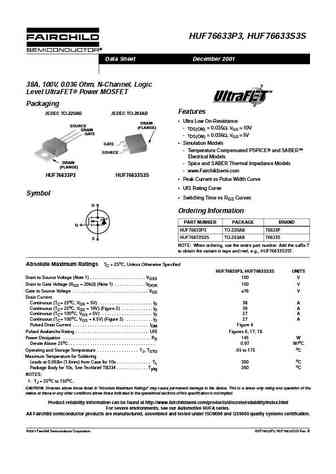

8.12. Size:223K fairchild semi

huf76633p3-s3s.pdf

HUF76633P3, HUF76633S3S Data Sheet December 2001 38A, 100V, 0.036 Ohm, N-Channel, Logic Level UltraFET Power MOSFET Packaging Features JEDEC TO-220AB JEDEC TO-263AB Ultra Low On-Resistance DRAIN SOURCE (FLANGE) - rDS(ON) = 0.035 , VGS = 10V DRAIN GATE - rDS(ON) = 0.036 , VGS = 5V Simulation Models GATE - Temperature Compensated PSPICE and SABER SOURCE El

8.13. Size:844K onsemi

huf76639s3s.pdf

Is Now Part of To learn more about ON Semiconductor, please visit our website at www.onsemi.com Please note As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor s system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclatur

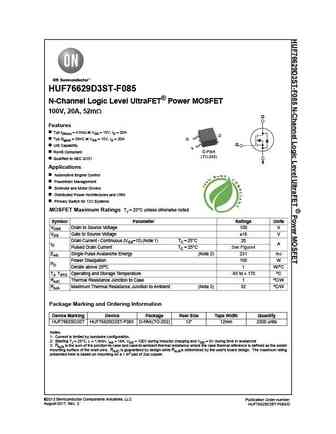

8.14. Size:428K onsemi

huf76629d3st-f085.pdf

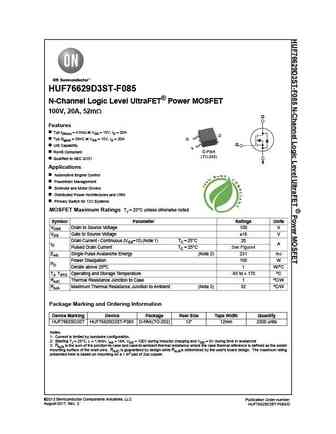

HUF76629D3ST-F085 N-Channel Logic Level UltraFET Power MOSFET 100V, 20A, 52m D Features Typ rDS(on) = 41m at VGS = 10V, ID = 20A Typ Qg(tot) = 39nC at VGS = 10V, ID = 20A G UIS Capability RoHS Compliant Qualified to AEC Q101 S Applications Automotive Engine Control Powertrain Management Solenoid and Motor Drivers Distributed Power Architectures and VRM Pr

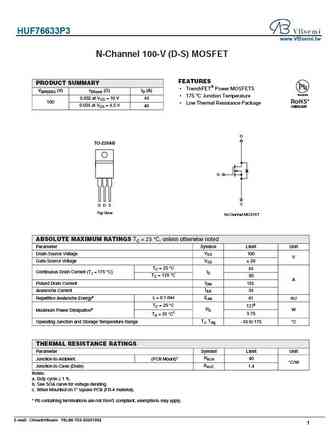

8.15. Size:843K cn vbsemi

huf76633p3.pdf

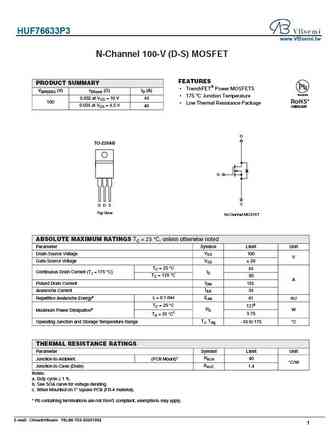

HUF76633P3 www.VBsemi.tw N-Channel 100-V (D-S) MOSFET FEATURES PRODUCT SUMMARY TrenchFET Power MOSFETS V(BR)DSS (V) rDS(on) ( )ID (A) Available 175 C Junction Temperature 0.032 at VGS = 10 V 45 RoHS* 100 Low Thermal Resistance Package 0.035 at VGS = 4.5 V 40 COMPLIANT D TO-220AB G S G D S Top View N-Channel MOSFET ABSOLUTE MAXIMUM RATINGS TC = 25 C,

Другие IGBT... HUF76407D3ST, HUF76419D3ST, HUF76419S3ST, HUF76429D3ST, HUF76429S3ST, HUF76437S3ST, HUF76439S3ST, HUF76445S3ST, IRF1407, HUF76619D3ST, HUF76629D3ST, HUF76633S3ST, HUFA75307D3, HUFA75307D3S, HUFA75307D3ST, HUFA75307P3, HUFA75309D3