STU420S MOSFET Equivalente. Reemplazo. Hoja de especificaciones. Principales características

Número de Parte: STU420S

Tipo de FET: MOSFET

Polaridad de transistor: N

ESPECIFICACIONES MÁXIMAS

Pdⓘ - Máxima disipación de potencia: 50 W

|Vds|ⓘ - Voltaje máximo drenador-fuente: 40 V

|Vgs|ⓘ - Voltaje máximo fuente-puerta: 20 V

|Id|ⓘ - Corriente continua de drenaje: 24 A

CARACTERÍSTICAS ELÉCTRICAS

Cossⓘ - Capacitancia de salida: 110 pF

RDSonⓘ - Resistencia estado encendido drenaje a fuente: 0.024 Ohm

Búsqueda de reemplazo de STU420S MOSFET

- Selecciónⓘ de transistores por parámetros

STU420S datasheet

stu420s std420s.pdf

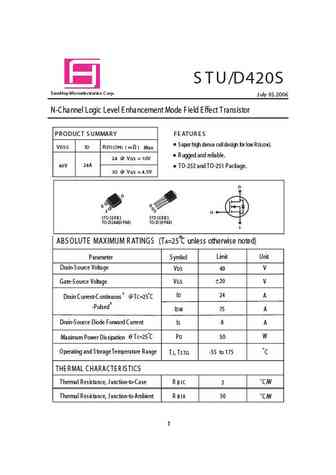

S TU/D420S S amHop Microelectronics C orp. July 05,2006 N-Channel Logic Level E nhancement Mode Field E ffect Transistor PR ODUC T S UMMAR Y FEATUR ES S uper high dense cell design for low R DS (ON). VDS S ID R DS (ON) ( m ) Max R ugged and reliable. 24 @ VGS = 10V 24A 40V TO-252 and TO-251 Package. 30 @ VGS =4.5V D D G S G STU SERIES STD SERIES TO-252AA(D-PAK) TO-251(l-PA

stu426s std426s.pdf

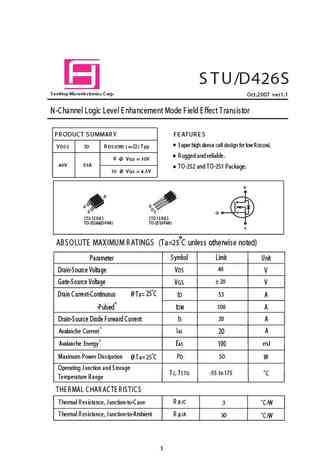

S TU/D426S S amHop Microelectronics C orp. Oct,2007 ver1.1 N-Channel Logic Level E nhancement Mode Field E ffect Transistor PR ODUCT S UMMAR Y FEATUR ES S uper highdense cell design for lowR DS (ON). Typ VDS S ID R DS (ON) ( m ) R ugged and reliable. 8 @ VGS =10V 40V 53A TO-252 and TO-251 Package. 10 @ VGS =4.5V D D G S G STU SERIES STD SERIES TO-252AA(D-PAK) TO-251(l-PAK)

stu421s std421s.pdf

Green Product STU/D421S SamHop Microelectronics Corp. Aug.20,2006 P-Channel Logic Level Enhancement Mode Field Effect Transistor PRODUCT SUMMARY FEATURES RDS(ON) ( m ) Max VDSS ID Super high dense cell design for low RDS(ON). Rugged and reliable. 45 @ VGS = -10V -40V -10A TO-252 and TO-251 Package. 60 @ VGS = -4.5V D D D G G G S S STU SERIES STD SERIES TO-252AA(D-PAK)

stu428s std428s.pdf

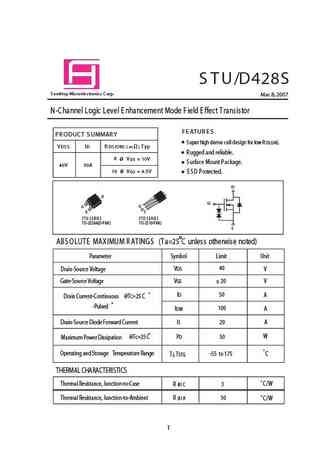

S TU/D428S S amHop Microelectronics C orp. Mar.8,2007 N-Channel Logic Level E nhancement Mode Field E ffect Transistor FEATUR ES PR ODUCT S UMMAR Y S uper high dense cell design for low R DS (ON). Typ VDS S ID R DS (ON) ( m ) R ugged and reliable. 8 @ VGS =10V Surface Mount Package. 40V 50A 10 @ VGS =4.5V ESD Protected. D D G G S STU SERIES STD SERIES TO-252AA(D-PAK) TO-

Otros transistores... STU432L , FCPF11N60NT , STU428S , FCPF13N60NT , STU426S , FCPF16N60NT , STU421S , FCPF22N60NT , P60NF06 , FCPF7N60 , STU419S , FCPF7N60NT , STU419A , FCPF9N60NT , STU417S , FDA032N08 , FDA15N65 .

History: STU421S | FDA16N50F109

History: STU421S | FDA16N50F109

🌐 : EN ES РУ

Liste

Recientemente añadidas las descripciónes de los transistores:

MOSFET: 2N7002KM | 2N7002KH | AON5802 | AOSS62934 | AOSN21319C | AONS66966 | AONR62992 | AON7400B | AON6578 | AO3480C | AO3400C | HAF1008S | HAF1008L | EMZB08P03H | CS30N20FA9R | AOT66613L

Popular searches

2n1306 transistor | 2sa750 datasheet | 2sa940 transistor datasheet | 2sb549 | 5n50 mosfet equivalent | a1016 transistor | a1693 transistor | a933 datasheet