HUF75329S3 Datasheet. Specs and Replacement

Type Designator: HUF75329S3 📄📄

Type of Transistor: MOSFET

Type of Control Channel: N-Channel

Absolute Maximum Ratings

Pd ⓘ - Maximum Power Dissipation: 94 W

|Vds|ⓘ - Maximum Drain-Source Voltage: 55 V

|Vgs|ⓘ - Maximum Gate-Source Voltage: 20 V

|Id| ⓘ - Maximum Drain Current: 49 A

Tj ⓘ - Maximum Junction Temperature: 150 °C

Electrical Characteristics

RDSonⓘ - Maximum Drain-Source On-State Resistance: 0.024 Ohm

Package: TO262AA

📄📄 Copy

HUF75329S3 substitution

- MOSFET ⓘ Cross-Reference Search

HUF75329S3 datasheet

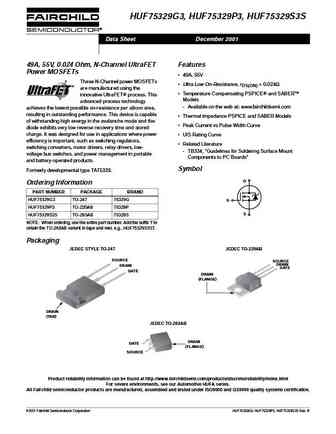

huf75329g3 huf75329p3 huf75329s3s.pdf

HUF75329G3, HUF75329P3, HUF75329S3S Data Sheet December 2001 49A, 55V, 0.024 Ohm, N-Channel UltraFET Features Power MOSFETs 49A, 55V These N-Channel power MOSFETs Ultra Low On-Resistance, rDS(ON) = 0.024 are manufactured using the Temperature Compensating PSPICE and SABER innovative UltraFET process. This Models advanced process technology - Available on t... See More ⇒

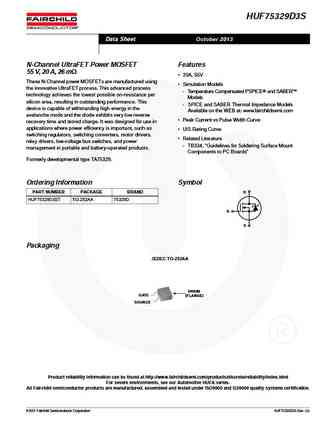

huf75329d3st.pdf

HUF75329D3S Data Sheet October 2013 N-Channel UltraFET Power MOSFET Features 55 V, 20 A, 26 m 20A, 55V These N-Channel power MOSFETs are manufactured using Simulation Models the innovative UltraFET process. This advanced process - Temperature Compensated PSPICE and SABER technology achieves the lowest possible on-resistance per Models silicon area, resulting in ou... See More ⇒

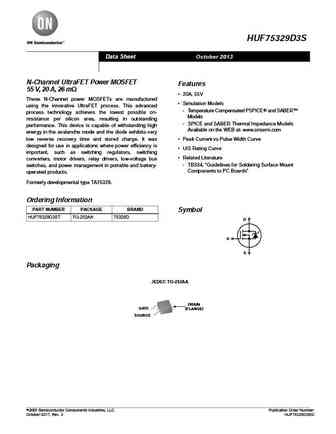

huf75329d3-s.pdf

HUF75329D3, HUF75329D3S Data Sheet December 2001 20A, 55V, 0.026 Ohm, N-Channel UltraFET Features Power MOSFETs 20A, 55V These N-Channel power MOSFETs Simulation Models are manufactured using the - Temperature Compensated PSPICE and SABER innovative UltraFET process. This Models advanced process technology - SPICE and SABER Thermal Impedance Models achieves the... See More ⇒

huf75329d3s.pdf

HUF75329D3S Data Sheet October 2013 N-Channel UltraFET Power MOSFET Features 55 V, 20 A, 26 m 20A, 55V These N-Channel power MOSFETs are manufactured Simulation Models using the innovative UltraFET process. This advanced - Temperature Compensated PSPICE and SABER process technology achieves the lowest possible on- Models resistance per silicon area, resulting in o... See More ⇒

Detailed specifications: HUF75321P3, HUF75321S3, HUF75321S3S, HUF75321S3ST, HUF75329D3, HUF75329D3S, HUF75329G3, HUF75329P3, AON7506, HUF75329S3S, HUF75329S3ST, HUF75332G3, HUF75332P3, HUF75332S3S, HUF75333G3, HUF75333P3, HUF75333S3

Keywords - HUF75329S3 MOSFET specs

HUF75329S3 cross reference

HUF75329S3 equivalent finder

HUF75329S3 pdf lookup

HUF75329S3 substitution

HUF75329S3 replacement

Need a MOSFET replacement? Our guide shows you how to find a perfect substitute by comparing key parameters and specs