FDG6322C Datasheet. Specs and Replacement

Type Designator: FDG6322C 📄📄

Type of Transistor: MOSFET

Type of Control Channel: NP-Channel

Absolute Maximum Ratings

Pd ⓘ - Maximum Power Dissipation: 0.3 W

|Vds|ⓘ - Maximum Drain-Source Voltage: 25 V

|Vgs|ⓘ - Maximum Gate-Source Voltage: 8 V

|Id| ⓘ - Maximum Drain Current: 0.22 A

Tj ⓘ - Maximum Junction Temperature: 150 °C

Electrical Characteristics

RDSonⓘ - Maximum Drain-Source On-State Resistance: 4 Ohm

Package: SC70

📄📄 Copy

FDG6322C substitution

- MOSFET ⓘ Cross-Reference Search

FDG6322C datasheet

fdg6322c.pdf

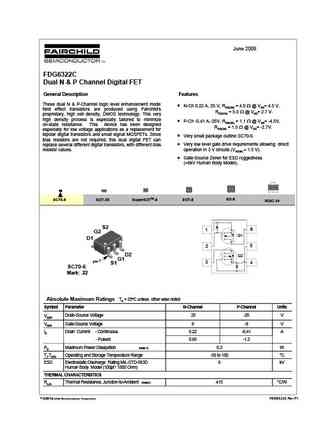

June 2008 FDG6322C Dual N & P Channel Digital FET General Description Features These dual N & P-Channel logic level enhancement mode N-Ch 0.22 A, 25 V, RDS(ON) = 4.0 @ VGS= 4.5 V, field effect transistors are produced using Fairchild's RDS(ON) = 5.0 @ VGS= 2.7 V. proprietary, high cell density, DMOS technology. This very high density process is especially tailored to minimiz... See More ⇒

fdg6322c.pdf

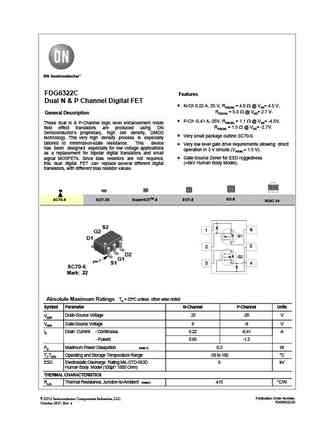

FDG6322C Features Dual N & P Channel Digital FET N-Ch 0.22 A, 25 V, RDS(ON) = 4.0 @ VGS= 4.5 V, RDS(ON) = 5.0 @ VGS= 2.7 V. General Description P-Ch -0.41 A,-25V, RDS(ON) = 1.1 @ VGS= -4.5V, These dual N & P-Channel logic level enhancement mode RDS(ON) = 1.5 @ VGS= -2.7V. field effect transistors are produced using ON Semiconductor's proprietary, high cell densit... See More ⇒

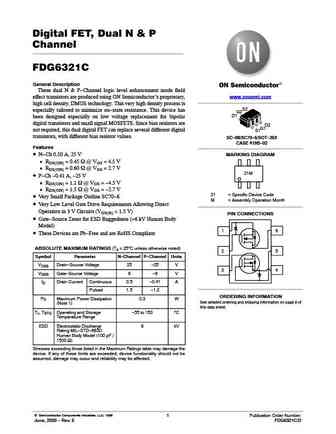

fdg6321c.pdf

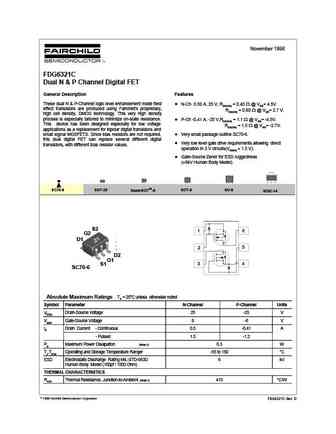

November 1998 FDG6321C Dual N & P Channel Digital FET General Description Features These dual N & P-Channel logic level enhancement mode field N-Ch 0.50 A, 25 V, RDS(ON) = 0.45 @ VGS= 4.5V. effect transistors are produced using Fairchild's proprietary, RDS(ON) = 0.60 @ VGS= 2.7 V. high cell density, DMOS technology. This very high density process is especially tailored to mi... See More ⇒

fdg6320c.pdf

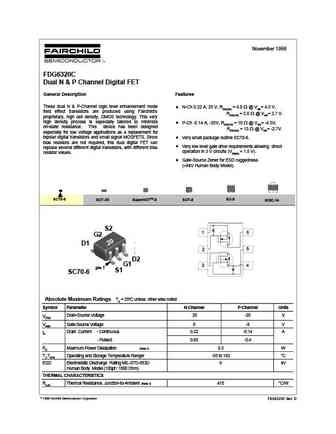

November 1998 FDG6320C Dual N & P Channel Digital FET General Description Features These dual N & P-Channel logic level enhancement mode N-Ch 0.22 A, 25 V, RDS(ON) = 4.0 @ VGS= 4.5 V, field effect transistors are produced using Fairchild's RDS(ON) = 5.0 @ VGS= 2.7 V. proprietary, high cell density, DMOS technology. This very high density process is especially tailored to mi... See More ⇒

Detailed specifications: FDG6316P, FDG6317NZ, FDG6318P, FDG6318PZ, FDG6320C, STS4501, FDG6321C, STS4300, 8N65, STS400, FDG6332C, STS3623, FDG6332CF085, STS3621, FDG6335N, FDG8842CZ, STS3620

Keywords - FDG6322C MOSFET specs

FDG6322C cross reference

FDG6322C equivalent finder

FDG6322C pdf lookup

FDG6322C substitution

FDG6322C replacement

Learn how to find the right MOSFET substitute. A guide to cross-reference, check specs and replace MOSFETs in your circuits.

MOSFET Parameters. How They Affect Each Other

History: STT01L10 | FDD4141-F085

🌐 : EN ES РУ

LIST

Last Update

MOSFET: CEZC2P07 | CEZ2R05 | CEU3133 | CES2361 | CES2312A | CEP100N10L | CEM3425 | CEM3139 | CEM3133 | CEM3115

Popular searches

2sc5242 | irf540 equivalent | mp1620 transistor equivalent | 2sc945 transistor | c2073 transistor | ac176 transistor | mpsa20 | irfp264